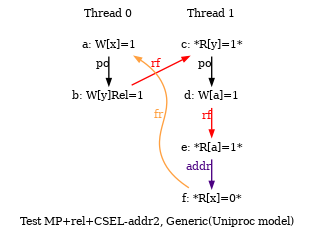

AArch64 MP+rel+CSEL-addr2

{

0:X10=x; 1:X10=x;

0:X2=y; 1:X2=y;

1:X3=z; 1:X6=1;

1:X4=a; 1:X5=b;

}

P0 | P1 ;

MOV W9,#1 | LDR W1,[X2] ;

STR W9,[X10] | CMP W1,#1 ;

MOV W11,#1 | CSEL X3,X4,X5,EQ ;

STLR W11,[X2] | STR W6,[X3] ;

| LDR W7,[X3] ;

| EOR W8,W7,W7 ;

| LDR W9,[X10,W8,SXTW] ;

Observed

1:X9=0; 1:X7=1; 1:X1=1;